RISC on a Chip: David Patterson and Berkeley RISC-I

David Patterson and team at UC Berkeley give RISC its name and make the first RISC microprocessor design.

If IBM pioneered RISC techniques, the 'RISC' name and the real impetus to make RISC mainstream came from the University of California, Berkeley with a team including David Patterson. Their work is still influential in designs we use today, including directly in the RISC-V architecture. Surprisingly, though, performance wasn't the initial motivation for the work at Berkeley.

In ‘The First RISC: John Cocke and the IBM 801’ we looked at the origins of what would later become known as RISC (for Reduced Instruction Set Computer). In the mid-1970s at IBM a small team working under the direction of John Cocke, built the first computer, the IBM 801, to fully adopt the RISC approach. Having leapt forward to look at the early years of the Acorn RISC Machine (which would later become Arm) architecture, we're going to travel back in time now to look at what happened next after the 801.

The objective of the 801 project was to build a machine that could help IBM compete with the highly successful series of minicomputers from Digital Equipment Corporation (DEC). By 1978, the 801 team had succeeded in building a design whose performance was much better than IBM's existing minicomputer line. The team continued to work on the design and developed a second improved version of the 801. However, IBM wouldn't rush to turn the technology into a stand-alone machine. The 801 would be used, for example as an input and output controller in the IBM 3090 mainframe, but that would only appear as late as 1985.

Outside IBM there were whispers about a mysterious new machine that IBM was developing, but the technology remained largely hidden from the outside world. John Cocke discussed some of the ideas more widely, and eventually an article on the 801 appeared in the Datamation computer magazine in 1979, but no papers or conference presentations were made about the 801 or the ideas that lay behind its design.

David Patterson and VAX

Competing with DEC’s minicomputers had motivated the IBM team to look for a fresh approach to computer architecture. It would be work on the next generation of DEC machines that would prompt the next stage in the development of the RISC concept.

David Patterson had studied computer science at the University of California, Berkeley and had written his PhD thesis on the formal verification of microprograms. Microprograms were programs written in microcode, the code that was used within the computer’s central processing unit to implement the instruction set architecture exposed to users.

In 1977, DEC launched VAX, its latest and most powerful series of minicomputer designs. Like IBM’s mainframes, the VAX had a complex instruction set (CISC) architecture and made extensive use of microcode.

With his interest in microcode, Patterson was offered a sabbatical at one of DEC's minicomputer facilities in Boxborough, Massachusetts, to help deal with bugs in the microcode of the VAX series. Working on the VAX’s microcode in the fall of 1979 convinced him that debugging microcode for a complex CISC instruction set was extremely challenging.

The KA780, the Central Processing Unit of the VAX 11/780 computer, had microcode in two places. It had 4k complex 96-bit long microcode instructions in a Read Only Memory and 2k microcode instructions in fast Random Access Memory. The microcode in RAM would be loaded into memory from a PDP-11 minicomputer, attached to the VAX, at startup.

The existence of microcode in RAM provided the opportunity to update the code after the VAX had been shipped, including fixing any bugs.

The end of the 1970s saw the launch of the first sixteen-bit microprocessors. As microprocessors added more complex instructions, firms were turning to microcode in order to implement their designs. Some firms, such as Zilog with the Z8000, clung on to non-microcoded designs, but as we saw in Captain Zilog Crushed, this was difficult and time consuming even for the most skilled designer. The two most successful microprocessor architectures of the 16-bit era, the Intel 8086 and the Motorola 68000, both made extensive use of microcode.

Patterson’s experience with the VAX convinced him that, as microprocessor architectures became more complex, their microcode designs would inevitably have bugs. With a minicomputer such as the VAX, these bugs could be corrected after shipping using the microcode in RAM. With microprocessors, where the microcode was hard coded on the CPU die, an update would mean replacing the whole chip, an inconvenient and expensive process.

So Patterson wrote a paper suggesting that microprocessors should have two types of microcode storage, broadly following the approach used in the VAX. ROM for the simplest and most often used instructions and a small amount of cache RAM for the more complex instructions.

The paper was rejected. Patterson has recalled the emphatic rationale for the rejection:

This is a stupid way to design computers. It doesn't make sense to design microprocessors this way and, with this extra RAM, and cost, and patching and the field. This is nuts.

Building RISC-I

A few months later, in the fall of 1980, Patterson started to teach a graduate level class that included work to design a microprocessor architecture. Instead of adopting the approach in the rejected paper, he tried an alternative. Complex instructions were omitted entirely, meaning that there was no need for microcode. With no microcode there would be no scope for microcode bugs and no need for RAM to cache microcode for more complex instructions.

Patterson, along with one of his students, David Ditzel, by then working at Bell Labs, had already written up the ideas in a paper, “The Case for the Reduced Instruction Set Computer”. Acknowledging the work of John Cocke at IBM (Cocke had even appeared on the Berkeley campus to discuss some of his ideas), the paper set out several reasons to favour the RISC approach, including easier and faster implementation, better use of chip area and speed. Crucially, Patterson and his colleagues had both invented the ‘RISC’ name for the approach and shared the ideas behind it more widely.

Patterson sent a copy of the paper 'The Case for a Reduced Instruction Set Computer' to friends that he had worked with on his sabbatical at DEC. In September 1980 a rebuttal emerged from the VAX team in the form of a paper 'Comments on "The Case for the Reduced Instruction Set Computer"'. The rebuttal largely rested on the absence of real hardware to support Patterson and Ditzel’s claims.

But Patterson, his colleague Carlo Séquin, and their students had already set about building a microprocessor based on RISC principles, initially known as ‘Gold’ and later as ‘RISC-I’. Building a physical microprocessor was only possible as the Defense Advanced Research Projects Agency (DARPA) had provided funding for a number of related projects including a silicon fabrication service (MOSIS) and a project to develop Computer Aided Design Tools.

In practice, the design proved to be too complex for the design tools running (perhaps somewhat ironically) on Berkeley's own VAX 11/780 minicomputer. The team was forced to rewrite the tools and work on RISC-I progressed slowly.

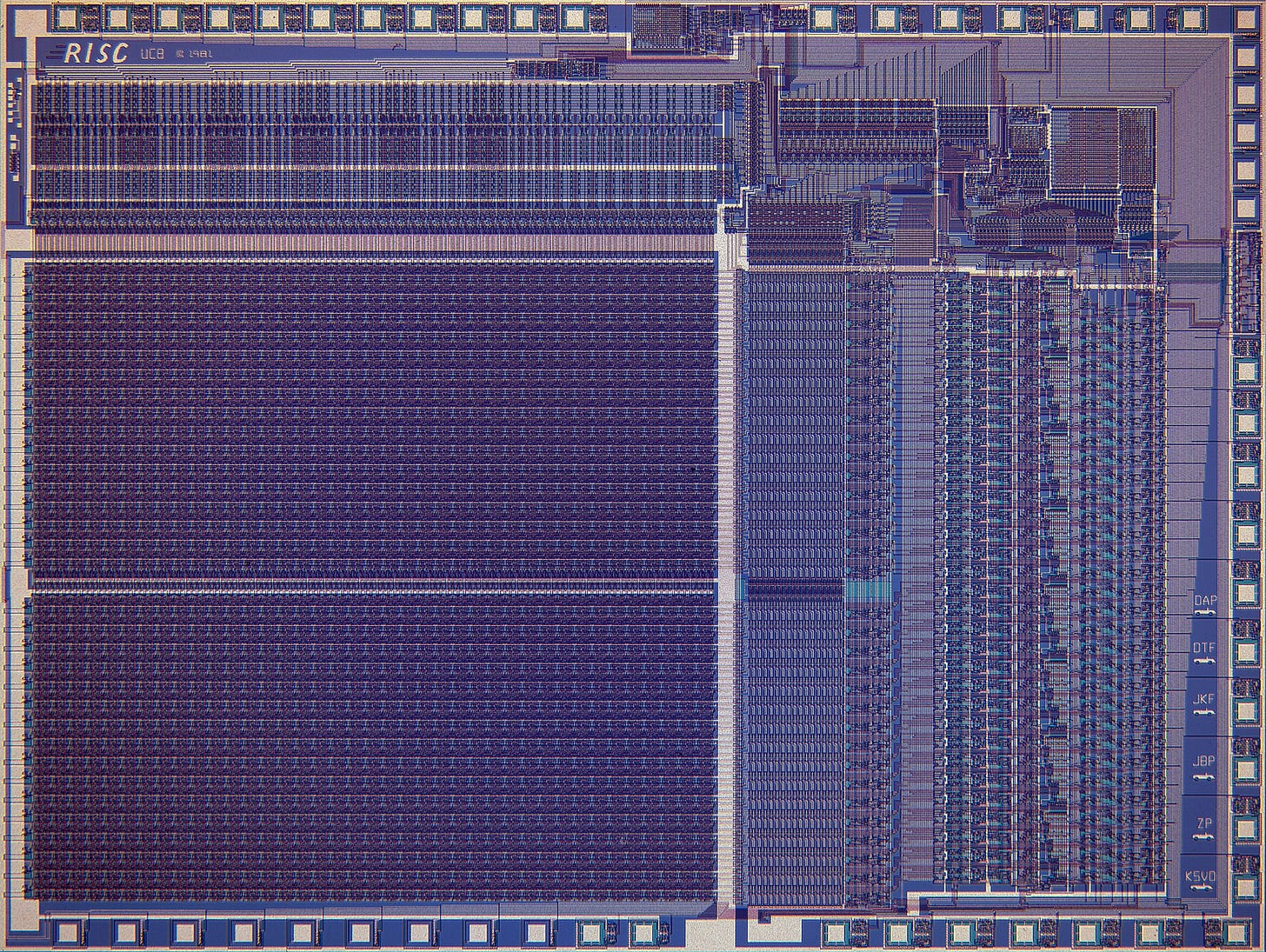

The RISC-I designs were finally sent to the fabrication service in June 1981. After a number of problems with the initial fabrication of the design, wafers with working chips only arrived back at Berkeley in May 1982. The Berkeley team used this to build a single board computer and were soon able to demonstrate it running c programs (although, the design had a bug in a single instruction that the compiler needed to be modified to avoid).

The RISC-I design used 44,500 transistors implemented using a 4 micron NMOS process with a relatively large die size of 10mm x 7.8 mm. Notably, because of the simple instruction set, only 6% of the die area was dedicated to either decoding instructions or control of the processor. In fact over half of the the transistors were dedicated to providing 78 physical 32-bit long general purpose registers.

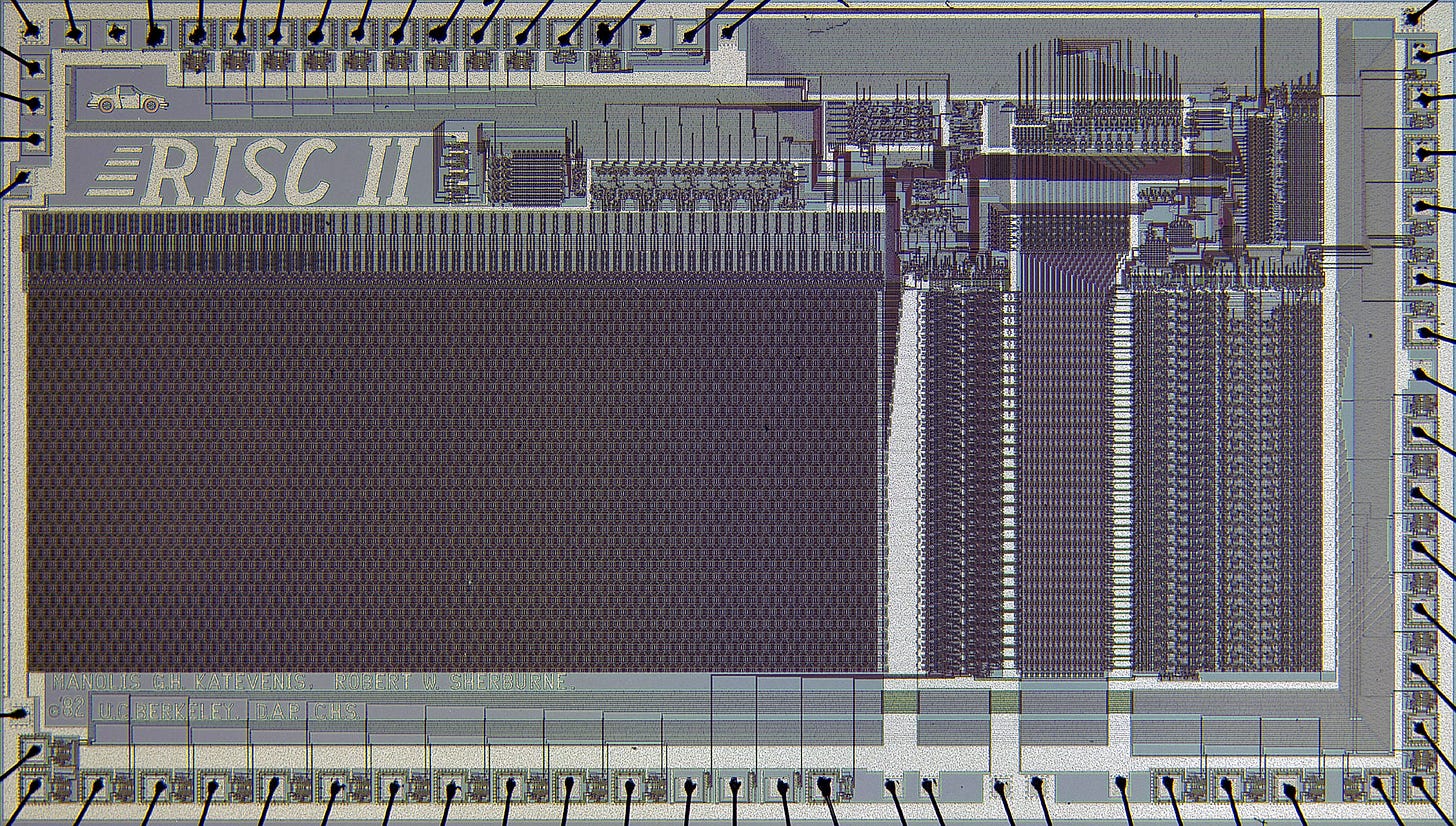

As work on RISC-I progressed, a second design, known as ‘Blue’ (later RISC-II) was started by two of Patterson’s students at Berkeley. RISC-II progressed more smoothly than RISC-I. The RISC-II design had even more registers than RISC-I, with 138 32-bit general purpose registers. It was able to implement them with a more economical design that used only 6 transistors per bit, rather than the 11 that had been used in RISC-I, so only needed 40,760 transistors were needed in total. It also used a more advanced 3 micron NMOS fabrication process.

RISC-I and RISC-II Performance

The original motivation for building RISC-I had been to avoid complex microcode but Patterson and his colleagues had expressed high hopes for the performance of the new design. Patterson and Séquin's paper summarising the initial results of the RISC project has a striking conclusion to it's abstract:

Preliminary benchmarks demonstrate the performance advantages of RISC. It appears possible to build a single chip computer faster than VAX 11/780.

The speed of the initial RISC-I chips was, though, in some respects disappointing. Some instructions performed as the Berkeley team expected but others were up to five times slower, an outcome that the team attributed to fabrication issues rather than the design.

A later paper set out the strong theoretical performance of the RISC-I (using simulations so as to correct for the fabrication issues) vs the VAX 11/780 and the Zilog Z8000 microprocessor in more detail.

RISC-II didn’t have the fabrication issues of RISC-I, and comfortably outperformed both the VAX and the most advanced microprocessor design of the era, the Motorola 68000. Now with results from real hardware, most of the challenges and scepticism, expressed by the DEC VAX team, had been answered.

These results were remarkable. The VAX 11/780 was a complex and expensive minicomputer. It was being beaten by RISC-I and RISC-II, which were single chip microprocessor designs.

The Berkeley team's papers on RISC were widely disseminated. Unsurprisingly, there would soon be an 'Cambrian explosion' of interest, investment and work on RISC designs. We’ll look at how RISC took off in our next post.

The RISC-I Architecture

So let's have a look at the RISC-I architecture in more detail.