Pico Pi RISC-V

Who better to make RISC-V widely available than Raspberry Pi?

This is a mostly free post, with a short bonus discussion on Raspberry Pi and RISC-V at the end for premium subscribers.

After the slightly downbeat tone of last week’s post on Intel and to celebrate reaching 15,000 subscribers - thank you! - I wanted to write something much more upbeat.

And then the perfect topic dropped into my news feed: the new Raspberry Pi Pico 2.

I know Raspberry Pi (RPi) has its detractors. Any discussion of an RPi Board is seemingly always accompanied by recommendations to buy something else, whether it’s another look-alike (e.g. one of the fruit-alike Banana Pi or Orange Pi) Arm board or the latest x86-based alternative from Intel. RPi lost a lot of goodwill over the pandemic when it prioritized business customers over hobbyists. Users always crave more performance, lower power consumption, and lower prices from their RPis.

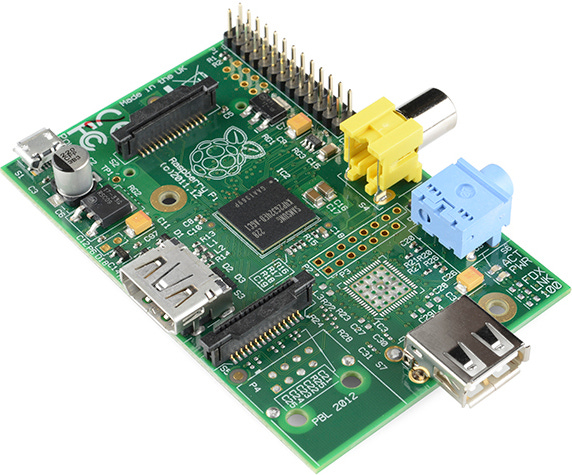

These complaints are the price of success. RPi effectively created a new category of computers. The name hasn’t quite become synonymous with small single-board computers, but it’s close. RPi is the benchmark that others are compared with. Under the leadership of founder Eben Upton, RPi has shipped 60 million computers since launching in 2012.

And RPi differs from its competitors in one key respect, it started with a mission:

… to put affordable computing in the hands of people all over the world.

after Upton realized that:

No one ever bought a games console, no one ever bought a mobile phone, and had that be their ladder into engineering and computer programming, in the same way that the BBC Micro was for me and for my friends.

So he set out to create a device that would be fun and also provide a ‘frictionless’ gateway to creativity. That was the first Raspberry Pi.

We can hear more about the history of RPi in this short video produced for the 10th anniversary of the launch of the first Pi.

Most recently RPi’s operating company - Raspberry Pi Ltd - was listed on the London Stock Exchange. With a market value of £700m (about $900m), Raspberry Pi Ltd is not - quite - a unicorn, but not every tech company needs to be a multibillion-dollar giant.

And the Raspberry Pi Foundation continues its charitable mission.

And really the dream is by the time we get to our 20th anniversary, that there will be nobody in the world who hasn't had the opportunity to have a low-cost, high-performance, general-purpose computing experience.

Pi Pico

RPi started with and is still best known for, its credit card-sized, Linux-capable, single-board computers. Today’s post, though, is about the latest version of the little microcontroller-based member of the Pi family, the Pi Pico.

The original Pi Pico was launched in 2020 with a price starting at less than $4. It used a microcontroller - the RP2040 - designed by RPi, their first custom silicon, and fabbed by TSMC. The RP2040 combined two Arm Cortex M0+ cores with some unique features, notably ‘Programmable Input/Output’ or ‘PIO’.

PIO allows you to create additional hardware interfaces, or even new types of interface. If you’ve ever looked at the peripherals on a microcontroller and thought “I need four UARTs and I only have two,” or “I’d like to output DVI video,” or even “I need to communicate with this accursed serial device I found, but there is no hardware support anywhere,” then you will have fun with PIO.

The Pi PICO is a much less powerful design than the original Pi and its successors. Each 32-bit Cortex M0+ runs at only 133MHz compared to 2.4GHz for the latest 64-bit ‘big’ Pi.

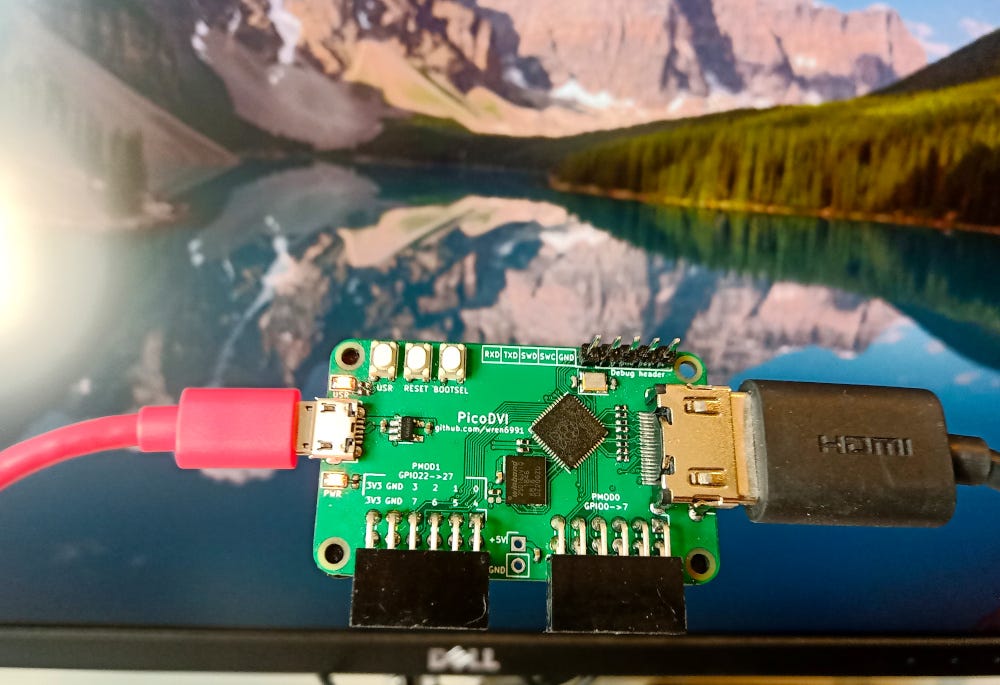

But with PIO the RP2040 has some impressive abilities. For example, in a demonstration first implemented by RPi’s Luke Wren, it can generate DVI video output, without needing additional video-controller hardware.

From the GitHub repository with the DVI code:

This project stems from a stupid idea I had during RP2040 bringup. I couldn't convince myself the idea was too stupid to work, so I took a leap of faith on it, and the results are documented here.

RP2040 was designed to run at 133 MHz, but we found (without too much surprise) that typical silicon can be pushed further…

With some of the core-local hardware on RP2040, and a neat encoding trick, I could do pixel-doubled TMDS encode on-the-fly using around 60% of an M0+ (running at 252 MHz, for 640x480p 60 Hz DVI).

Essentially, one of the overclocked Cortex M0+ cores is fast enough to generate the signal needed for DVI output, leaving the other core free to run user programs.

This all makes me nostalgic for the Sinclair ZX80 which used a humble 8-bit Zilog Z80 and some simple custom circuitry to generate its display. Except there was only one Z80 so you could have a display or run your program but not both.

Pi Pico 2

Then, earlier this August, Raspberry Pi announced the second version of the Pi Pico. The Pi Pico 2 uses another RPi-designed microcontroller - the RP2350 - that provides several upgrades over the original Pi Pico.

Dual Arm Cortex M33 cores running at 150MHz replacing the dual Arm Cortex M0+ cores;

The Cortex M33 adds single-precision floating point and DSP (Digital Signal Processing) instructions;

3 PIO blocks instead of 2 in the RP2040.

Arm provides CoreMark benchmark results for the M0+ (2.33) and the M33 (4.09)so the M33 should be a significant performance upgrade compared to the M0+.

All these upgrades have been achieved without changing the form factor making the Pico 2 a potential ‘drop-in’ replacement for the original Pico.

Jeff Geerling has a great video introducing the Pico 2 and comparing it with the original Pico.

A little RISC-V

If you’ve watched Jeff Geerling’s video, you’ll have spotted the most intriguing feature of the RP2350: the inclusion of two RISC-V cores. These RISC-V cores - named Hazard3 - were designed in-house by the same Luke Wren who developed the original Pico’s DVI video capabilities. The source code for these cores is open-source and available to browse on GitHub. From that GitHub repository:

Hazard3 is a low-area, high-performance RISC-V processor with a 3-stage in-order pipeline.

As we saw in RISC-V: Origins and Architecture the RISC-V ISA consists of a base ISA plus extensions.

The cores used in the RP2350 adds lots of standard RISC-V extensions to the RV32I 32-bit base ISA:

M: Integer multiply/divide/modulo instructions;

A: Atomic memory operations;

C: Compressed 16-bit instructions (equivalently spelled Zca);

Zba: Address generation instructions;

Zbb: Basic bit manipulation instructions;

Zbs: Single-bit manipulation instructions;

Zbkb: Basic bit manipulation for scalar cryptography;

Zcb: Basic additional compressed instructions;

Zcmp: Push/pop and double-move compressed instructions;

Zicsr: CSR access instructions;

Debug, Machine, and User execution modes;

Physical Memory Protection Unit (PMP);

External debug support with four instruction address triggers.

And, taking advantage of the ability to add custom extensions to the standard RISC-V ISA, the RP2350 enables several Hazard3 custom extensions, including:

Xh3power: Power management instructions;

Xh3bextm: Bit-extract-multiple instruction;

Xh3irq: Local interrupt controller with nested, prioritized IRQ support;

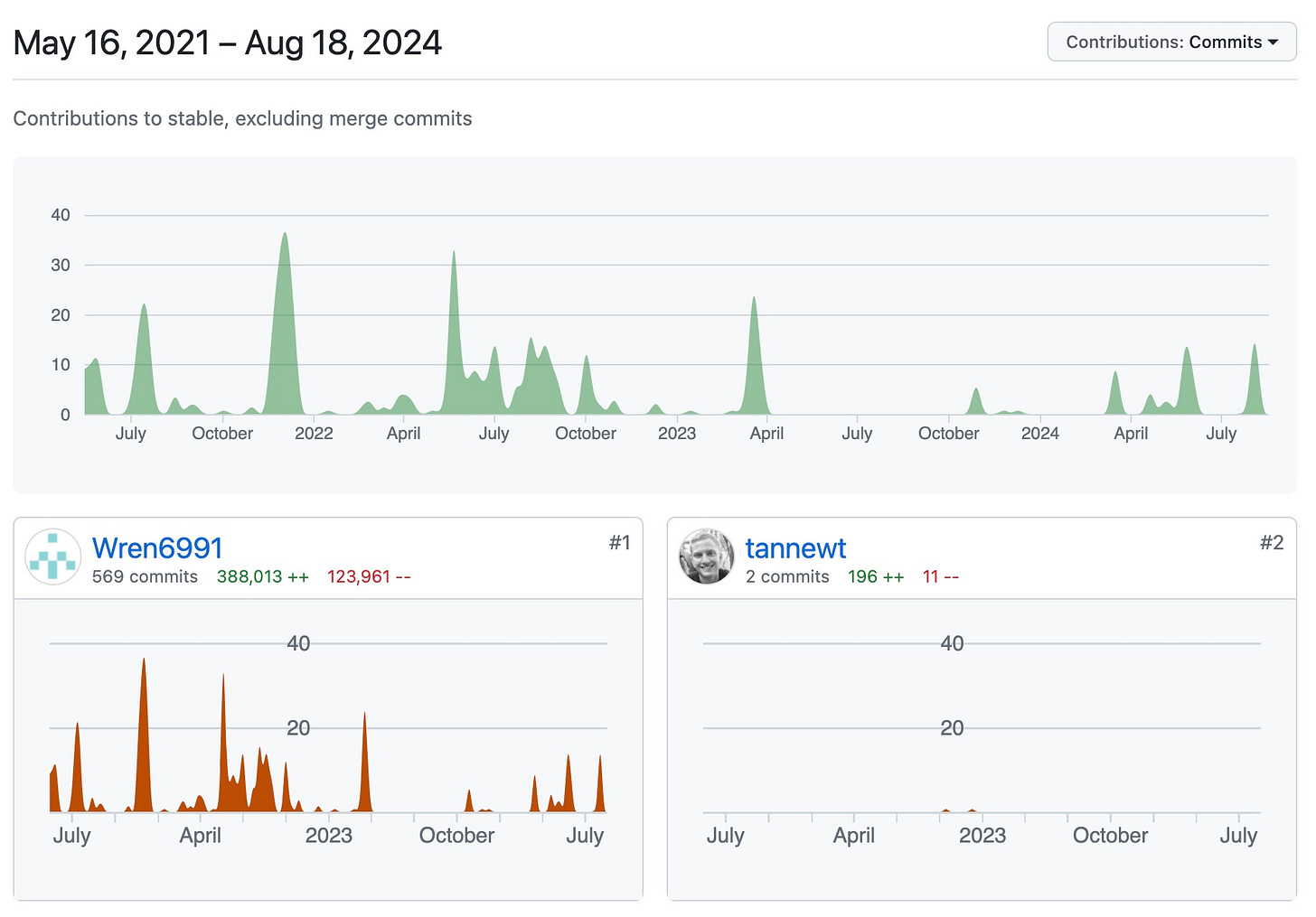

How fast is the Hazard3 and how does this compare to the Cortex M33? From the GitHub Repo:

The RP2350 configuration of Hazard3 achieves 3.81 CoreMark/MHz.

This is not quite at the level of the Cortex M33, but still pretty impressive. Especially as examination of the GitHub repo shows that Hazard3 is largely a solo effort over three years with 569 of the 575 commits coming from Luke Wren.

How are the RISC-V cores used in the Pico 2? At boot time the RP2350 can enable either two M33 cores, two RISC-V cores, or one of each.

And Luke Wren has already updated his video driver code to run on the RISC-V cores.

All Arm assembly in

libdvihas been ported to RISC-V and tuned for Hazard3

Pico microcontroller, Large interest

I’m - possibly irrationally - excited by the Pico 2.

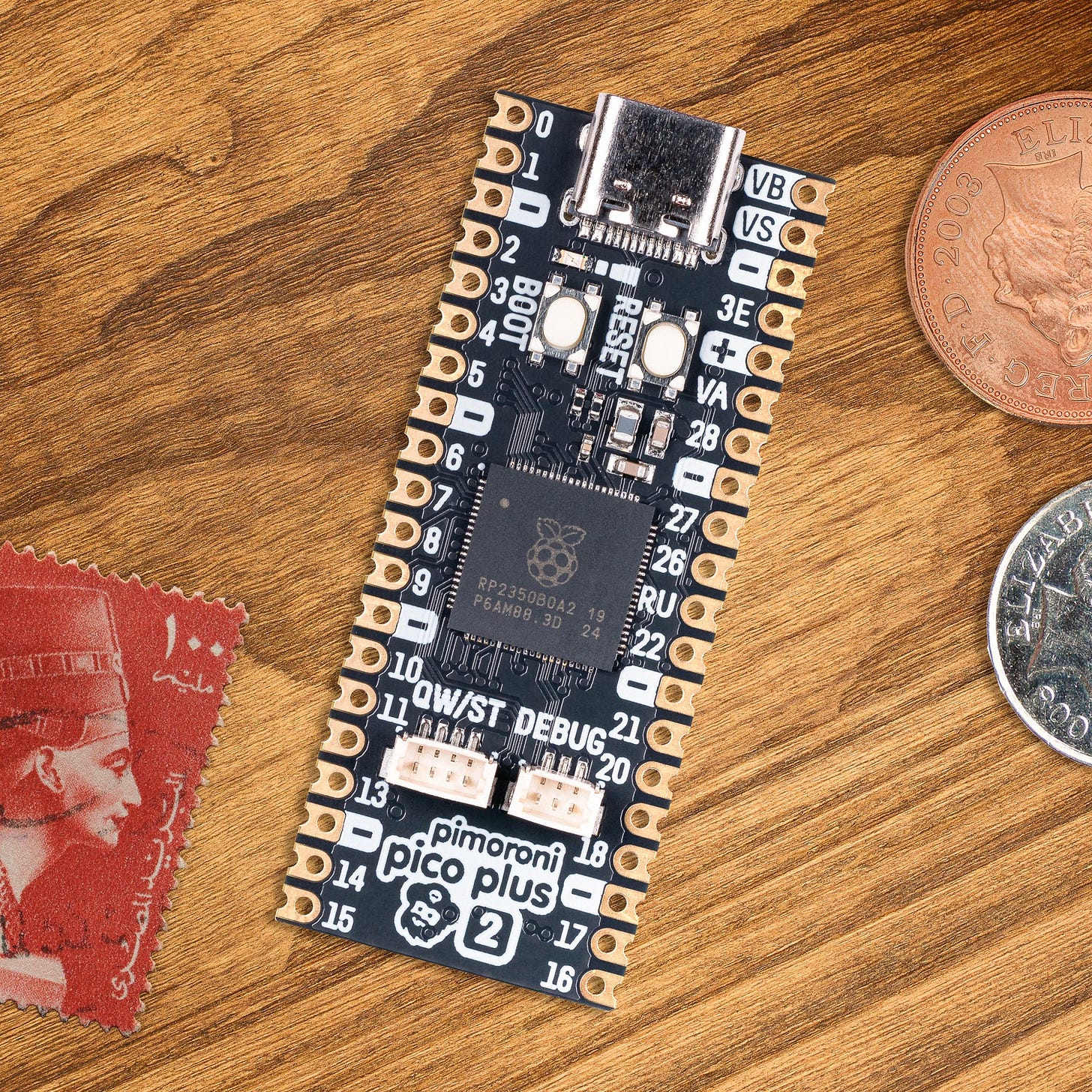

I’ve got a Pimoroni Pico Plus 2 Board on order - with a huge 16MB of Flash and 8MB of Pseudo-static RAM.

In an era when all we sometimes seem to read about is big tech firms spending tens of billions on GPU server farms, it’s great to see innovation on a much smaller scale.

Whether using a CPU to ‘bit-bang’ video or the homegrown RISC-V cores the Pico 2 has lots of these small-scale useful but fun features.

Why take a RISC-V?

This leaves one question. Why did RPi add RISC-V cores? Jeff Geerling asks the question at the end of his video.

Is it a signal that people should start transitioning their code to RISC-V?

We'll see.

Let’s consider some possible reasons for including these cores and see if we can come to any conclusions. Is Arm on RPi doomed?