Seven Projects Innovating Around RISC-V

Spanning the full range from huge chips for AI to virtual cores in Minecraft.

In One Year On. Thank You! I mentioned that I had a few changes planned to sharpen the focus of The Chip Letter. One of these changes is to ‘Chip Letter Links’ posts, which have, every couple of weeks, shared a range of links of interest. These posts have often been fun, but sometimes I’ve felt that the topics covered may have seemed a little … well, maybe random?

So in future these ‘links’ posts will have a common theme. Something that draws each of the links together. It might be a company, an architecture, a programming language or just an approach to doing computing.

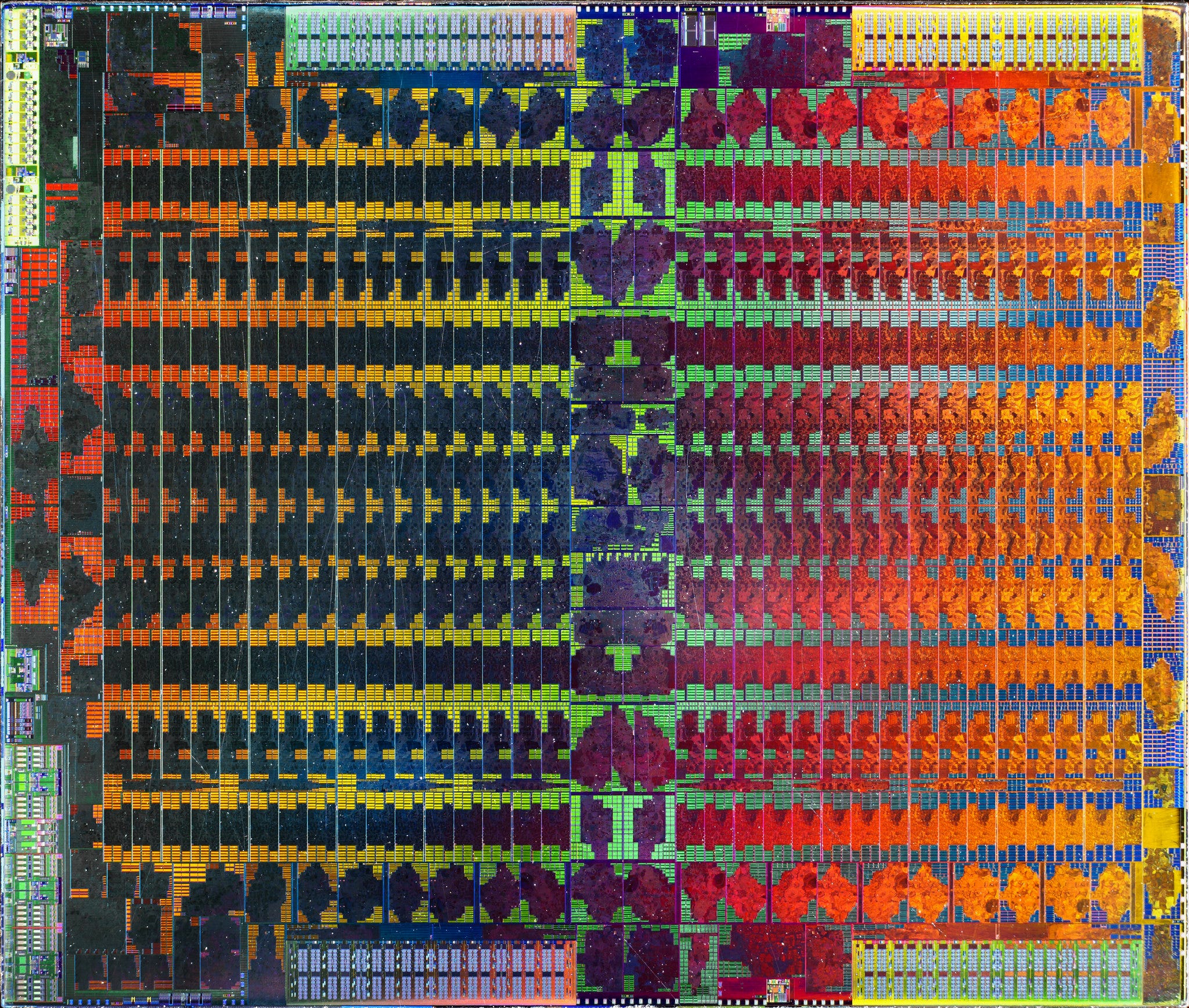

The ‘Chip Letter Link’s name will be retired but, I’ll try to keep the die shots that have started each post, this time an AMD Radeon Fiji GPU, from Fritzchens Fritz, which is perhaps my favourite die shot so far!

So on with today’s post, which is about …

Innovating Around RISC-V

One could argue that the most important test of the success of RISC-V is not whether the architecture grabs market share from existing architectures, but rather whether it helps to spurs innovation.

This isn’t necessarily around processor design. RISC-V is in many senses an ‘old-school’ RISC ISA with some refinements, so it may not drive future innovations in CPU design. Rather, it's about innovation around the processor design itself, or about enabling projects that would otherwise have been more difficult or expensive.

So I thought it would be interesting to have a look at a few RISC-V projects that could claim to be innovating around the RISC-V architecture.

They are a mix of the highly commercial and the extremely fun. They range from startups with tens of millions of dollars of funding, to hobby projects to build ‘virtual cores’ that run in online games. From projects that aim to be at the cutting edge of AI to those with a ‘retro’ flavour.

What they all have in common is that designers will all have had a copy of the RISC-V ISA specification open on their desktop for extended periods. One could argue, in some cases, that if RISC-V didn't exist then maybe they would have developed their own ISA. It’s certain, though, that in each case that the existence of RISC-V saved the designers effort and it’s use has made the project more accessible to others.

Let’s start with the more ambitious and serious, and then move on to the more fun projects.

P.S. Do please share if you have your own favourite project that is innovating around RISC-V. Comments can only be accessed by paying subscribers but everyone can just reply to this email if you’d like to share a less well known project. It would be great to do a sequel!

Esperanto

Esperanto sits at the intersection of two groups of startups: RISC-V (with SiFive, Tenstorrent, Ventana etc) and AI accelerators (with Cerebras, GraphCore etc).

It has a pedigree that is second to none. Dave Ditzel, its founder and executive chairman was co-author, with David Patterson, of the original Berkeley RISC paper. He may have had an extended period in the RISC wilderness working on x86 designs at Intel and Transmeta, but he’s now returned to his Berkeley RISC roots.

The company was founded in 2014 and has, so far, raised around $65m.

So what makes Esperanto innovative?

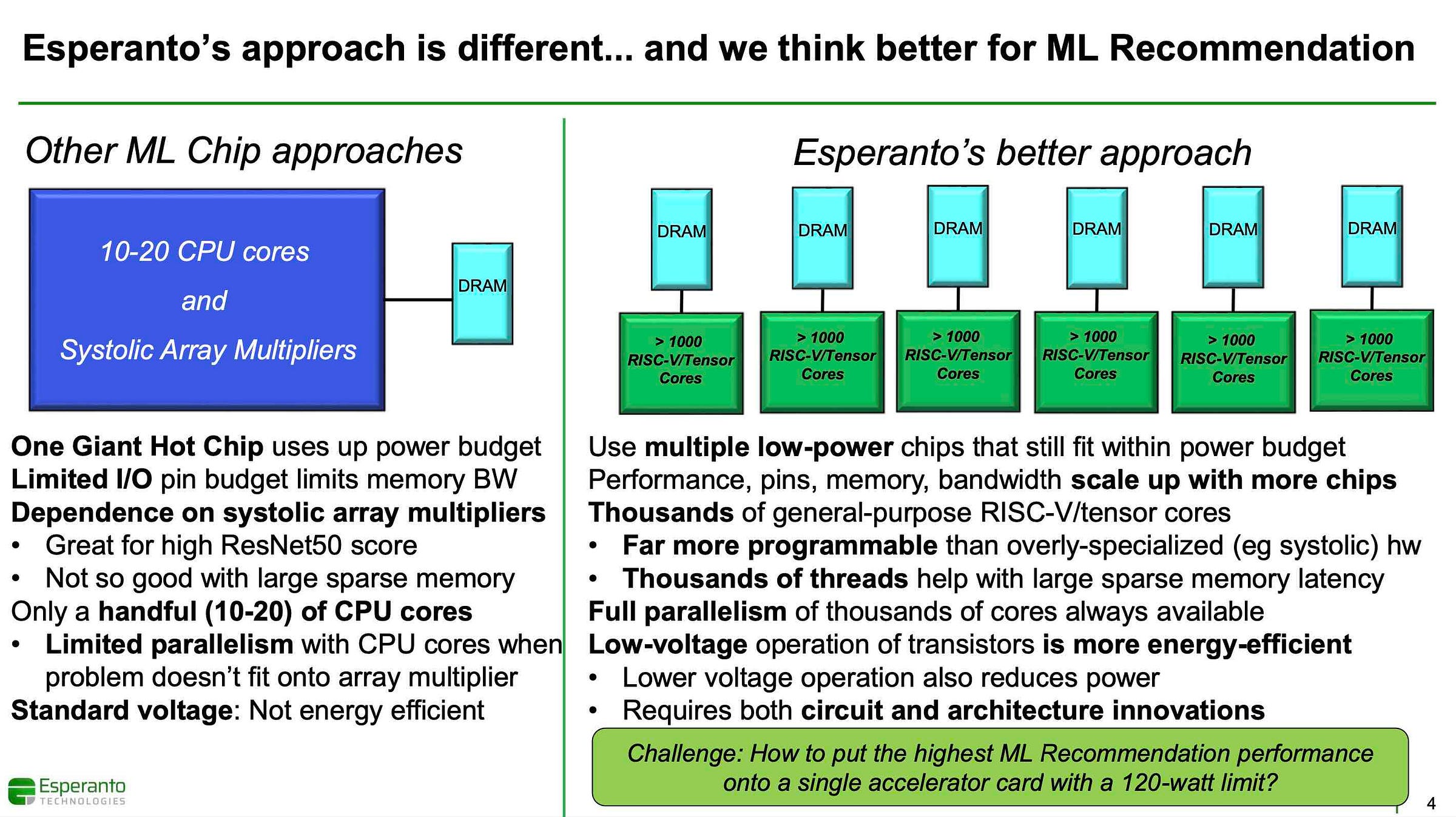

Here is a slide that contrasts their approach with other machine learning accelerators.

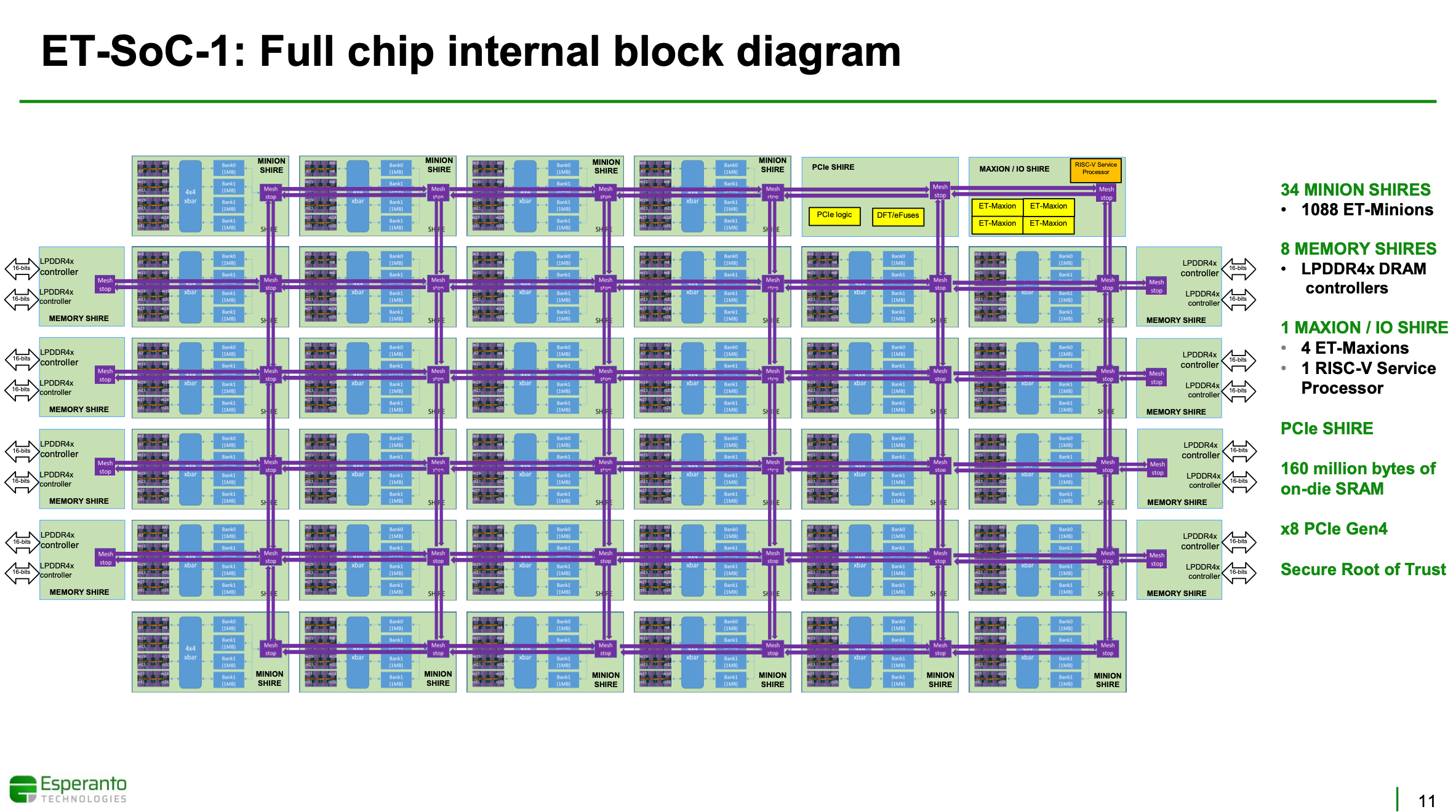

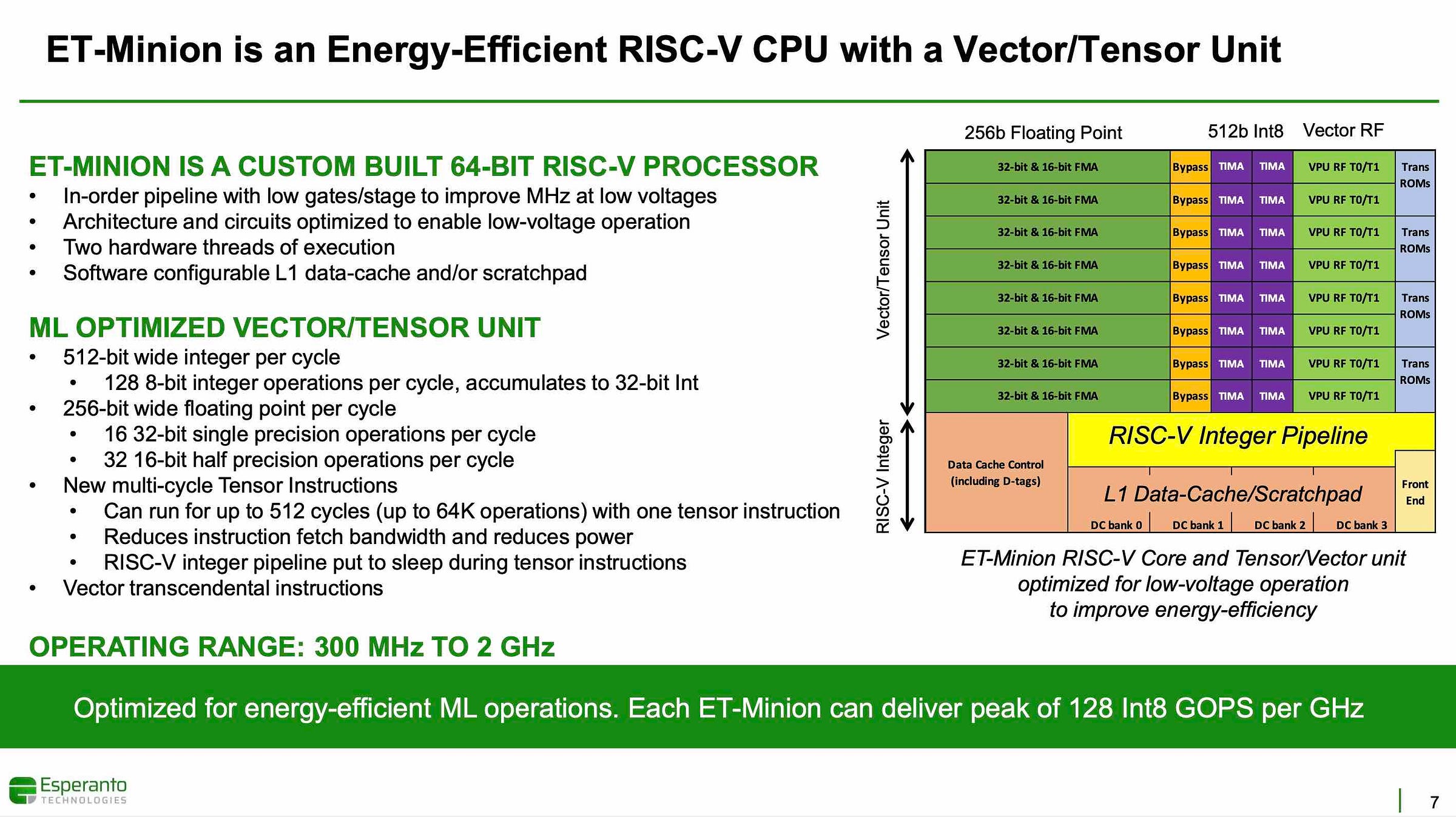

It’s using lots and lots of RISC-V cores. To be specific, over a thousand of its ‘Minion’ cores, each with a vector/tensor unit, on a single die, arranged into groups of ‘Minion Shires’. Here they are laid out on the Esperanto’s ET-SoC-1 Chip.

The ‘Minion’ cores themselves are built for low voltage operation and have a low gate count - something that is probably enabled by the simplicity of the RISC-V ISA.

For a fuller explanation, here is Dave Ditzel talking about ET-SoC-1 at Stanford in 2022 and here is a detailed presentation from Hot Chips 33.

In 2022 Esperanto claimed that:

The Esperanto ET-SoC-1 is the highest performance commercial RISC-V chip announced so far.

› It has the most 64-bit RISC-V cores on a single chip.

› It has the most RISC-V aggregate instructions per second on a single chip.

› It has the highest number of TOPS on a chip driven by RISC-V cores.

› Esperanto’s low-voltage technology provides differentiated RISC-V processors with the best performance per watt.

I’m more than a bit sceptical about whether these new accelerators will become mainstream (outside of Google’s TPU). You could argue that the Esperanto chip is just another design in a long series that have tried to cram lots of simple CPU cores onto a single die.

What strikes me, though, about Esperanto is how they have achieved this with so little funding. $65m dollars really doesn’t sound like much at all for a project like this that has built real silicon on TSMC 7nm and which has been running since 2014. I’m sure part of the reason for this is their ability to leverage RISC-V.

LMARV -1 (Learn Me A RISC-V version 1)

What is innovative, though, is how Robert has been able build such a simple design using discrete components for what is a mainstream architecture. He’s also, of course, been able to share his work on the project openly.

The next project goes back to the days of building computers from discrete components. It’s a project from Robert Baruch which Robert describes as:

The LMARV-1 (Learn Me A Risc-V, version 1) is a RISC-V processor built out of MSI and LSI chips. You can point to pieces of the processor and see the data flow. It should be a nice way of demonstrating how RISC-V works and how simple it is to implement.

There is an accompanying series of YouTube videos that discuss the design (which is a reboot of an earlier version) in detail.

The project is archived now and not under active development.

I guess you could argue that the project is a regression rather than innovation?

What is innovative, though, is how Robert has been able build such a simple design using discrete components for what is a mainstream architecture. He’s also, of course, been able to share his work on the project openly.

The code for LMARV-1 is available here.

After the break, RISC-V custom extensions in a very cheap microcontroller, a new kind of arithmetic implemented in a core in India, the smallest RISC-V processor and RISC-V in Minecraft!

The rest of this edition is for paid subscribers. If you value The Chip Letter, then please consider becoming a paid subscriber. You’ll get additional weekly content, learn more and help keep this newsletter going!

Ten Cent RISC-V Microcontroller

not Tencent RISC-V!

Does being extremely cheap, count as innovative? Being cheap certainly enables innovation elsewhere.

A few months ago EEVBlog had a video on a ‘ten cent’ (yes that’s really 10c) RISC-V microcontroller from a Chinese company called WCH.

I think it’s fair to say that EEVBlog’s David Jones gave the CH32V003 a review that was pretty positive.

“It looks as good as any mainstream processor. Hats off”

There are certainly cheaper microcontrollers, but few if any with this level of processing power.

So what powers this little Microcontroller? The QingKe (the internet tells me that this means ‘in no time’ but perhaps native speakers could confirm or correct me in this) V2 RISC-V processor, which is designed by WCH in-house, and which here runs at 48MHz.

QingKe V2 series microprocessor is a 32-bit general-purpose MCU microprocessor based on the standard RISC-V instruction set RV32I subset RV32E, with only 16 general-purpose registers, half of RV32I, and a more streamlined structure for deep embedded scenarios. V2 series supports standard RV32EC instruction extensions, in addition to custom XW extensions, Hardware Prologue/Epilogue (HPE), Vector Table Free (VTF), a more streamlined single-wire serial debug interface (SDI), and support for "WFE" instructions. (Source)

It’s interesting that a core as cheap as this should have custom extensions - called XW - something that wouldn't be possible with a licensed Arm core. Sadly, the only information I could find on XW (from the QingKe V2 manual) was:

XW: 16-bit compression instruction for self-extending byte and half-word operations

Which sounds useful, if not world changing.

Finally, to show how engaged WCH are with the RISC-V world, here is technical director Patrick Yang, with RISC-V co-funder Yunsup Lee.

Posits in RISC-V

A great example of a group trying something new out on a real core, that would have not been possible using mainstream commercial architectures.

We’re now going to return to AI and the topic of ‘posits’. First of all, what is or are posits? It’s all about AI and numbers. IEEE Spectrum explains:

Training the large neural networks behind many modern AI tools requires real computational might … Engineers think they have figured out a way to ease the burden by using a different way of representing numbers.

Posits were developed by John L. Gustafson and Isaac Yonemoto. According to their paper:

A new data type called a posit is designed as a direct drop-in replacement for IEEE Standard 754 floating-point numbers (floats). Unlike earlier forms of universal number (unum) arithmetic, posits do not require interval arithmetic or variable size operands; like floats, they round if an answer is inexact. However, they provide compelling advantages over floats, including larger dynamic range, higher accuracy, better closure, bitwise identical results across systems, simpler hardware, and simpler exception handling.

Posits are actually the latest version of Gustafson’s Unum (Universal Number) format. And they seems to have generated a lot of interest.

Other teams are working on their own hardware implementations to advance posit usage. “It’s doing exactly what I hoped it would do; it’s getting adopted like crazy,” Gustafson says. “The posit number format caught fire, and there are dozens of groups, both companies and universities, that are using it.”

So with its extensibility RISC-V would seem like an ideal base to use to look at the practical issues around implementation of posits. Enter PERI, a core that uses the SHAKTI RISC-V project, from the Indian Institute of Technology, as a base.

The article provides insights on how the Single-Precision Floating Point (“F”) extension of RISC-V can be leveraged to support posit arithmetic. We also present the implementation details of a parameterized and feature-complete posit Floating Point Unit (FPU).

The posit FPU has been integrated with the RISC-V compliant SHAKTI C-class core as an execution unit.

The paper then goes on to consider how posits compare with IEEE-754 floating point and to consider how to integrate with other RISC-V cores:

The article further highlights the specific differences between posit and IEEE-754 in view of RISC-V and thereby concludes that posit simplifies designing of floating-point arithmetic significantly.

We also present an alternate methodology of exploiting the custom space of RISC-V ISA to integrate the posit FPU as an accelerator with any RISC-V core supporting a RoCC like interface.

Note that this isn’t the first time that RISC-V has been used as the base for work on posits - the Clarinet project was first - but I think it’s first in integrating with a mainstream core like SHAKTI.

A great example of a group trying something out on a real core, that would have not been possible using mainstream commercial architectures.

SERV - The SErial RISC-V CPU

… it’s possible to fit 8 RISC-V cores into a single cheap FPGA chip

How small can a 32-bit core be? For the answer we can turn to SERV. According to the project’s README.

SERV is an award-winning bit-serial RISC-V core

In fact, the award-winning SERV is the world's smallest RISC-V CPU. It's the perfect companion whenever you need a bit of computation and silicon real estate is at a premium.

Apart from being the world's smallest RISC-V CPU, SERV also aims at being the best documented RISC-V CPU. For this there is an official SERV user manual with block diagrams that are correct to the gate-level, cycle-accurate timing diagrams and an in-depth description of how things work.

For an introduction, see this presentation ‘32-bit is the new 8-bit’ from developer Olof Kindgren.

To answer our original ‘how small’ question, it’s possible to fit 8 RISC-V cores into a single cheap FPGA chip!

RISC-V in Minecraft and Terraria

We’re going to end with a couple of games where users have built RISC-V processors inside the game itself.

The video demonstrations really speak for themselves. First, in Minecraft:

Then in Terraria:

Don’t try to do this at home for x86!

That’s it for this edition.

Thanks so much for supporting The Chip Letter.

Hello! Thank you for the insightful article. ‘QingKe’ (青稞 in Chinese) translates literally to ‘highland barley’. I tried to find more about the deeper meaning behind the name online, but couldn’t pinpoint it. Hope this information is helpful!